Ansys Clock FX mengevaluasi semua jalur jam di SoC untuk jitter jam yang disebabkan oleh Variasi Kebisingan Pasokan.

Ansys Clock FX memungkinkan Anda menghitung jitter jam dengan variasi pada SoC lengkap, tanpa mengambil jalan pintas apa pun. Pemodelan selnya yang unik memberikan waktu akurasi SPICE untuk tegangan atau kondisi variasi apa pun dengan satu perpustakaan. Clock FX memiliki arsitektur yang sepenuhnya berulir dan terdistribusi, dengan kemampuan untuk menskalakan hingga ribuan CPU.

Ansys Clock FX secara otomatis mengidentifikasi dan mensimulasikan semua jalur jam dalam suatu desain dan dapat memperhitungkan semua kontributor penting terhadap jitter jam di setiap jalur di berbagai proses, voltase, sudut suhu, dan skenario.

Ansys Clock FX adalah tambahan pada alur sign-off yang ada, dengan kinerja yang diperlukan untuk mengevaluasi semua jalur jam di SoC untuk jitter jam bahkan pada desain terbesar sekalipun.

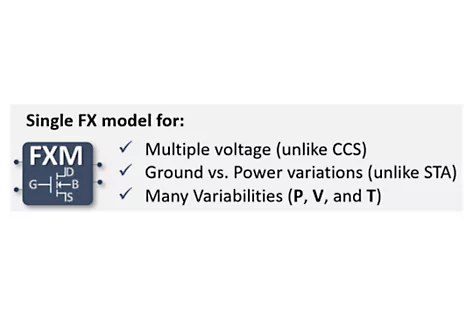

Pengaturan waktu berbasis jalur jam Clock FX untuk penundaan dan jitter dapat secara otomatis mengidentifikasi dan mensimulasikan setiap jalur jam dalam desain Anda. Ini memperhitungkan semua kontributor penting terhadap jitter jam di berbagai proses, voltase, sudut suhu, dan skenario. Clock FX memanfaatkan model transistor SPICE untuk membuat karakterisasi perpustakaan tunggal yang menggunakan propagasi bentuk gelombang penuh untuk memberikan akurasi SPICE dan menganalisis semua efek variabilitas dengan benar tanpa jalan pintas.

Pengaturan waktu tingkat SPICE berkapasitas tinggi menggunakan pemodelan sel yang sadar akan variabilitas proses, tegangan, dan suhu yang unik:

Ansys Clock FX menambang penurunan tegangan dinamis pada jaringan jam yang diproduksi oleh RedHawk-SC untuk menghitung jitter jam dengan akurasi tingkat SPICE. Clock FX memperhitungkan analisis multi-voltase yang akurat dan mensimulasikan dampak penundaan variasi pasokan pada jalur jam.

Ansys Clock FX secara otomatis mengidentifikasi dan mensimulasikan semua jalur jam dalam desain menggunakan model sel standar atau model SPICE tingkat transistor. Propagasi bentuk gelombang penuhnya memberikan akurasi yang diperlukan untuk mendapatkan hasil yang andal pada tegangan sangat rendah dan proses lanjutan.

Ansys Clock FX menangani efek level transistor seperti penurunan tegangan dan pantulan ground secara terpisah. Hal ini memungkinkan pengaturan waktu yang akurat pada tegangan ultra rendah dengan margin yang sangat tipis dan variabilitas yang parah.

Ansys Clock FX memanfaatkan model transistor SPICE dan propagasi bentuk gelombang penuh untuk memberikan akurasi yang diperlukan guna mendapatkan hasil yang andal pada tegangan sangat rendah untuk proses tingkat lanjut. Kapasitansi Miller dan efek lainnya ditangani dengan benar, tanpa jalan pintas.

Ansys Clock FX di-thread dan didistribusikan, secara signifikan mengurangi waktu penyelesaian dan kebutuhan memori, dibandingkan dengan Monte Carlo SPICE

Ansys Clock FX terintegrasi erat dengan alat analisis daya sign-off Ansys RedHawk-SC untuk mendapatkan penurunan tegangan dinamis untuk simulasi. Ini menghasilkan serangkaian laporan jitter yang mencakup berbagai jenis jitter.

Sangat penting bagi Ansys agar semua pengguna, termasuk penyandang disabilitas, dapat mengakses produk kami. Karena itu, kami berusaha untuk mengikuti persyaratan aksesibilitas berdasarkan US Access Board (Pasal 508), Panduan Aksesibilitas Konten Web (WCAG), dan format Templat Aksesibilitas Produk Sukarela (VPAT) saat ini.

AKR Tower – 9th Floor

Jl. Panjang no. 5, Kebon Jeruk

Jakarta Barat 11530 – Indonesia